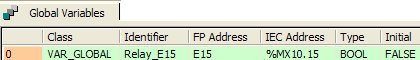

FP address: E15

IEC address: %MX10.15

Error alarm flags (E) are only available for FP2SH/FP10SH.

Description

Error alarm flags are designed to facilitate the analysis of error conditions and to record errors. Therefore in the special data registers a buffer has been defined so that the user has access to information about errors and their occurrence, including the actual number of error flags in the TRUE state, the order they were set to TRUE and the time at which the first error flag was set to TRUE.

When an error flag is set to TRUE by the error alarm program because the corresponding error situation has arisen, the number of error flags in the TRUE state stored in special data register DT90400 increases by one each time an error occurs. Flag numbers will be stored in sys_iErrorAlarm1RelayNumber...sys_iErrorAlarm19RelayNumber in the order that they were set to TRUE. If at least one of the error alarm flags E0 through E2047 is set to TRUE, sys_bIsErrorAlarmRelayOn will be set to TRUE. The time at which the first error alarm flag was set to TRUE is stored in sys_wErrorAlarm1MinSec, sys_wErrorAlarm1DayHour and sys_wErrorAlarm1YearMon.

Restrictions

There is no limit to the number of times an error alarm flag can be used in a program. However, if one error alarm flag is used with different error conditions in more than one error alarm program it will not be possible to accurately determine the nature of the error. The CPU does not check for multiple use.

When the power is turned OFF or when switching between PROG and RUN, the error flags as well as the affected special data registers are held. To reset the error flags and the special data registers, you have to press up the initialize/test switch in PROG mode.

However, system register Error alarm flag (E) of the group Act on error can be set to Clear to ensure that no error alarm flags are turned FALSE when the initialize/test switch is pressed up. Then only the next download of the program will reset the error flags and the corresponding special data registers.

The diagram below illustrates the internal structure and address assignment in the special data register area of this error buffer.

Global variables

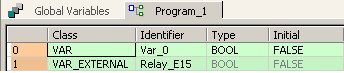

POU header

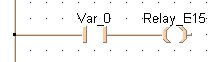

LD body

Error alarm diagram

- (1) sys_iNumberOfErrorAlarms: number of alarms that have occurred

- (2) sys_iErrorAlarm1RelayNumber...sys_iErrorAlarm19RelayNumber: error alarm flags stored in the order they were set to TRUE

- (3) Error alarm E15 is set to TRUE

- (4) Time at which the first error alarm flag was set to TRUE: sys_wErrorAlarm1MinSec: second and minute data

sys_wErrorAlarm1DayHour: hour and day data

sys_wErrorAlarm1YearMon: month and year data

sys_bIsErrorAlarmRelayOn : TRUE when one of the error alarm flags E0–E2047 is TRUE

Because in Control FPWIN Pro all write operations on error flags are internally compiled into SET and RST instructions, all write operations to an error flag affect the special internal flag R9040 and the special data registers DT90400 to DT90422.

When all error alarm flags are set to FALSE, sys_bIsErrorAlarmRelayOn will be set to FALSE.

To monitor alarm flags using Control FPWIN Pro: or evaluate the system variables of alarm flags.