When processing networks in the LD or FBD editor, the following evaluation order applies:

The compiler starts at the top left at the power rail. If the elements are directly connected to the power rail, the current is conducted through all of these elements. If there are no directly connected elements, the compiler starts with all inputs. Control FPWIN Pro7 deals with inputs as though they were ready for processing.

Then the compiler looks for the element at the highest level which it can evaluate. If there are two elements on the same level (line), it processes the left element first. If the element is an output or the cue for a function or function block, the compiler creates the corresponding code. Temporary variables can be inserted from the compiler in order to buffer the signal or stack it.

In the case of the element from the second step (interim result), the compiler conducts the output current to all elements directly connected to it. Then it evaluates the next element. Finally, it returns to the second step until all elements are evaluated or no element is available for the evaluation.

The processing procedure is interrupted or ended.

Below are several examples for the executing order in Control FPWIN Pro7.

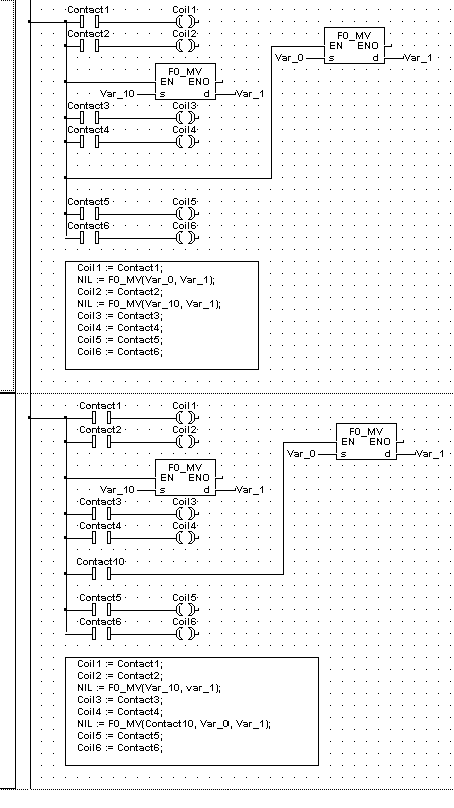

Example 1:

Example 2:

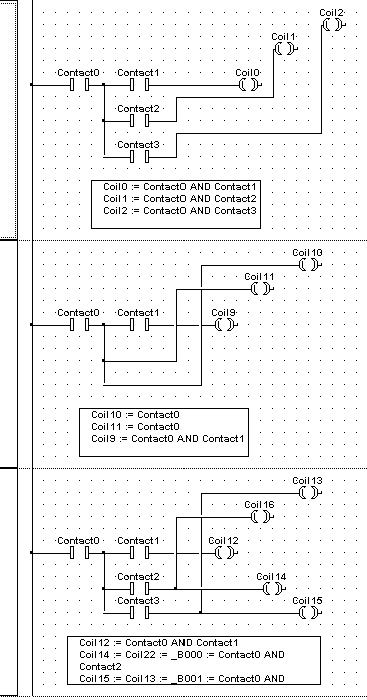

Example 3:

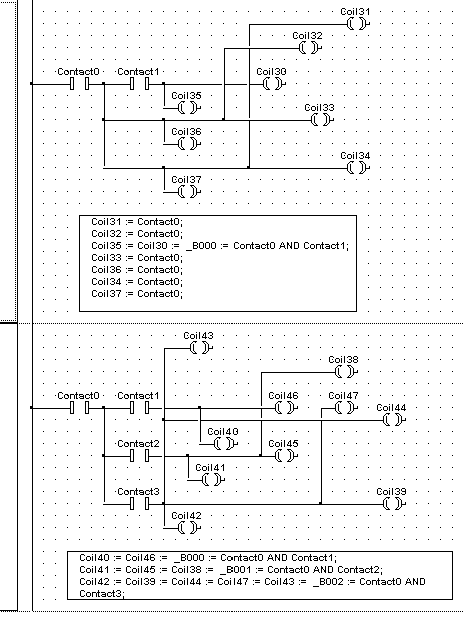

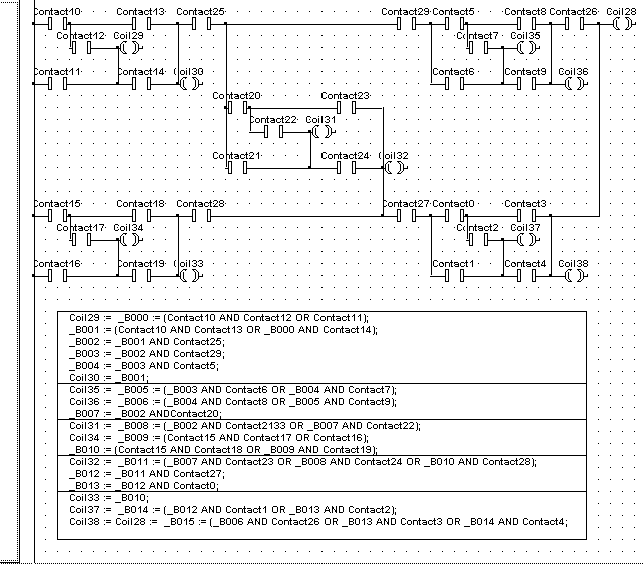

Example 4: